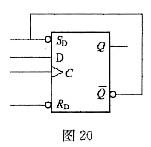

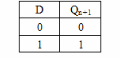

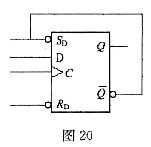

触发器D如图20所示,可以判定触发器的状态是( )。A、不变 B、置1 C、计数 D、置0

题目

B、置1

C、计数

D、置0

相似考题

参考答案和解析

更多“触发器D如图20所示,可以判定触发器的状态是( )。”相关问题

-

第1题:

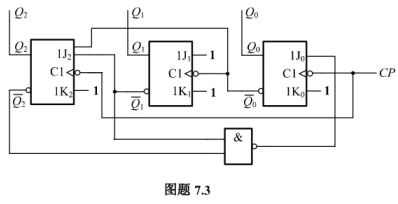

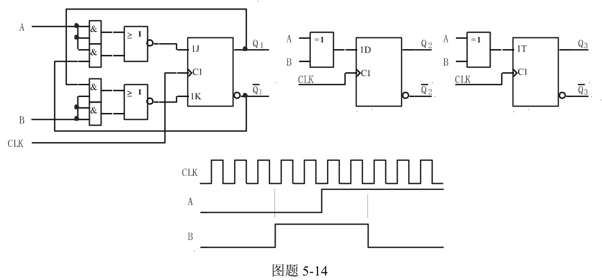

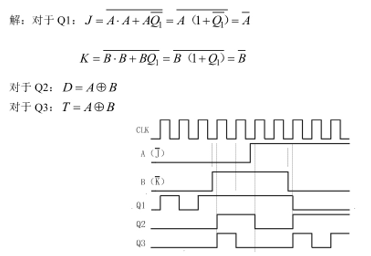

计数器电路如图题7.3所示。设各触发器的初始状态均为“0”,要求:

(1) 写出各触发器的驱动方程和次态方程;

(2)画出次态卡诺图;画出状态转换图并说明该计数器电路的逻辑功能;

参考答案:

参考答案:

-

第2题:

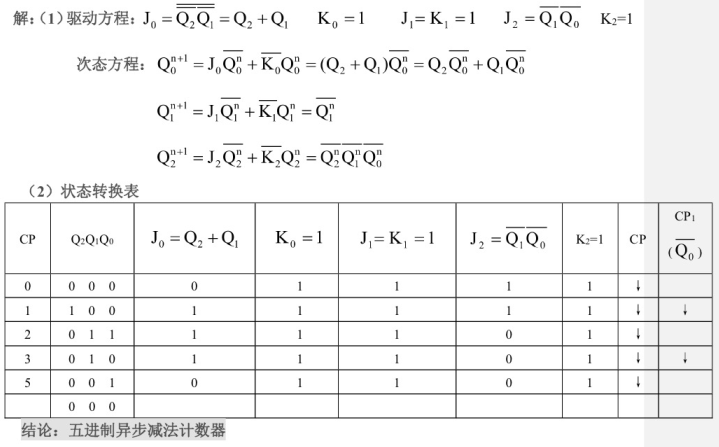

试画出图题5-14所示各触发器输出Q端的波形,CLK、 A和B的波形如图所示。(设Q初始状态为0)

答案:

答案:

-

第3题:

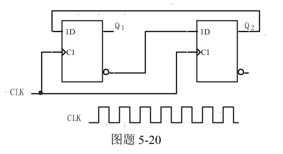

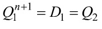

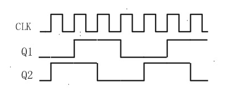

试画出图题5-20所示电路中触发器输出Q1、Q2端的波形,CLK的波形如图所示。(设Q初始状态为0)

答案:

答案:

-

第4题:

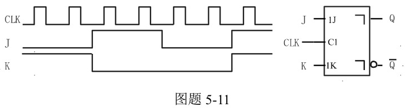

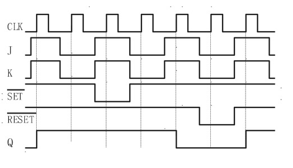

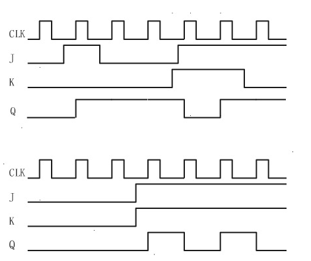

画出图题5-11所示的脉冲JK触发器输出Q端的波形,输入端J K与CLK的波形如图所示。(设Q初始状态为0)

答案:

答案:

-

第5题:

试画出图题5-19所示电路中触发器输出Q1、Q2端的波形,输入端CLK的波形如图所示。(设Q初始状态为0)

答案:

答案:

-

第6题:

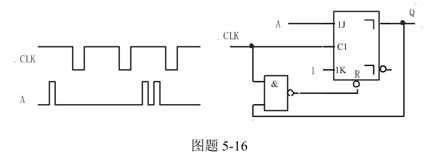

试画出图题5-16所示触发器输出Q端的波形,CLK 的波形如图所示。(设Q初始状态为0)

答案:

答案:

-

第7题:

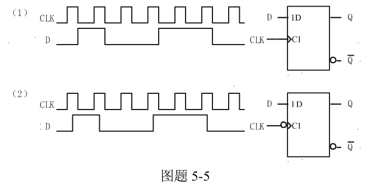

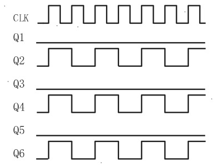

画出图题5-5所示的边沿触发D触发器输出端Q端的波形,输入端D与CLK的波形如图所示。(设Q初始状态为0)

答案:

答案:

-

第8题:

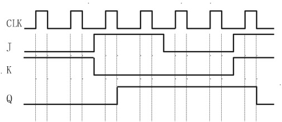

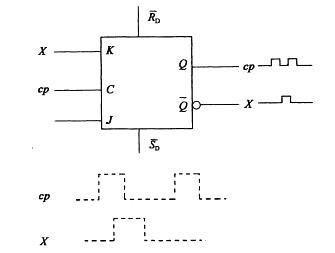

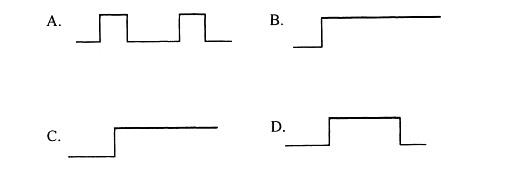

JK触发器及其输入信号波形如图所示,该触发器的初值为0,则它的输出Q为:

答案:B解析:图示电路是电位触发的JK触发器。当cp=1时,触发器取输入信号JK。触发器的状态由JK触发器的功能表(表格略)确定。

答案:B解析:图示电路是电位触发的JK触发器。当cp=1时,触发器取输入信号JK。触发器的状态由JK触发器的功能表(表格略)确定。 -

第9题:

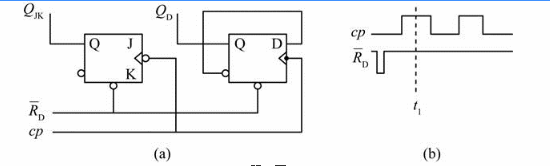

图(a)所示电路中,复位信号及时钟脉冲信号如图(b)所示,经分析可知,在t1时刻,输出QJK和QD分别等于( )。

附:D触发器的逻辑状态表为:

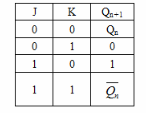

JK触发器的逻辑状态表为: A.00

A.00

B.01

C.10

D.11答案:B解析:电路开始工作,复位信号进行了复位,则D触发器和JK触发器的初始输出都为零,即Q=0,

。根据图可知,D触发器是上升沿触发,JK触发器是下降沿触发。因此,第一个上升沿时只有D触发器被触发,则D触发器的输出QD变为1,而JK触发器的输出QJK保持不变还是0。因此,t1时刻,QJK=0,QD=1。 -

第10题:

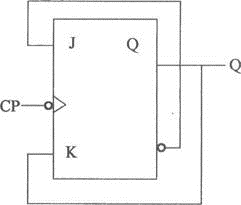

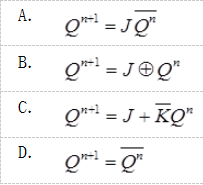

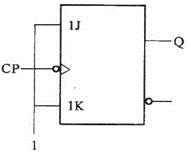

JK触发器外部连接如图所示,则其输出可表达为( )。

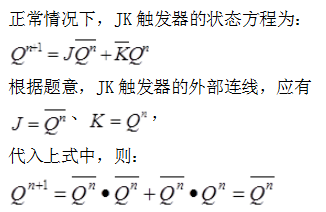

答案:D解析:

答案:D解析:

-

第11题:

JK触发器构成的电路如图所示,该电路能实现的功能是( )。

A.RS触发器

A.RS触发器

B.D触发器

C.T触发器

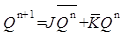

D.T′触发器答案:C解析:正常情况下,JK触发器的状态方程为

当J=K=1时,则

为T触发器。 -

第12题:

在如图7-72所示的RS触发器,设Q的初始状态为1,当输入X信号后,输出Q为()。

A.X B.X C.1 D.0答案:C解析:正确答案是C。

提示:任何触发器当没有CP脉冲时,都保持原状态。 -

第13题:

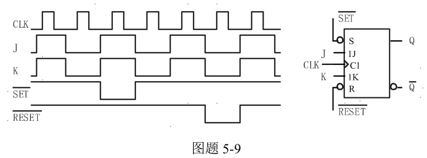

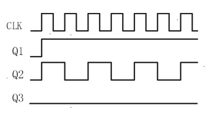

画出图题5-9所示的正边沿触发JK触发器输出Q端的波形,输入端J、K与CLK的波形如图所示。(设Q初始状态为0)

答案:

答案:

-

第14题:

试画出图题5-15所示各触发器输出Q端的波形,CLK 的波形如图所示。(设Q初始状态为0)

答案:

答案:

-

第15题:

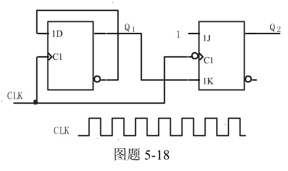

试画出图题5-18所示电路中触发器输出Q1、Q2端的波形,CLK的波形如图所示。(设Q初始状态为0)

答案:

答案:

-

第16题:

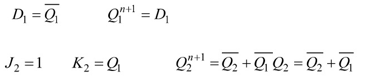

画出图题5-10所示的JK触发器输出端Q端的波形,CLK的波形如图所示。(设Q初始状态为0)

答案:

答案:

-

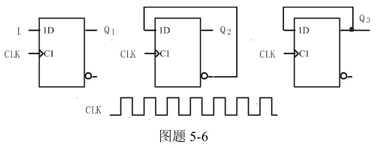

第17题:

画出图题5-6所示的边沿D触发器输出Q端的波形,CLK的波形如图所示。(设Q初始状态为0)

答案:

答案:

-

第18题:

画出图题5-8所示的JK触发器输出Q端的波形,输入端JK与CLK的波形如图示。(设Q初始状态为0)

答案:

答案:

-

第19题:

触发器D如图20所示,可以判定触发器的状态是( )。 A、不变

A、不变

B、置1

C、计数

D、置0答案:C解析:D的输入总是与输出状态相反,时钟脉冲过后,输出变成原相反状态,所以是计数 -

第20题:

逻辑电路如图所示,当A=“0”,B=“1”时,C脉冲来到后,D触发器应( )。

A.具有计数功能

A.具有计数功能

B.保持原状态

C.置“0”

D.置“1”答案:A解析:“=1”为异或门的逻辑符号,即F=ab+ab -

第21题:

JK触发器及其输入信号波形图如图所示,该触发器的初值为0,则它的输出Q为:

答案:A解析:解:选A。

答案:A解析:解:选A。

由JK触发器的真值表可以得到答案。 -

第22题:

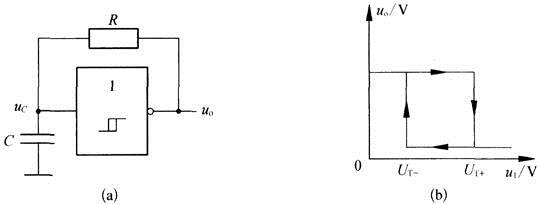

CMOS集成施密特触发器组成的电路如图(a)所示,该施密特触发器的电压传输特性曲线如图(b)所示,该电路的功能为( )。

A. 双稳态触发器

A. 双稳态触发器

B. 单稳态触发器

C. 多谐振荡器

D. 三角波发生器答案:C解析:

施密特触发器属于“电平触发型”电路。它们的输入、输出特性是当输入电压u1上升到UT+电平时,触发器翻转,输出负跳变;过了一段时间,输入电压回降到UT+电平时,输出并不回到初始状态,直到输入u1继续下降到UT-电平时,输出才翻转至高电平(正跳变)。用公式:UT+-UT-=△UT表示,△UT称为施密特触发器的滞后电压。施密特触发器和电阻、电容组成多谐振荡器。 -

第23题:

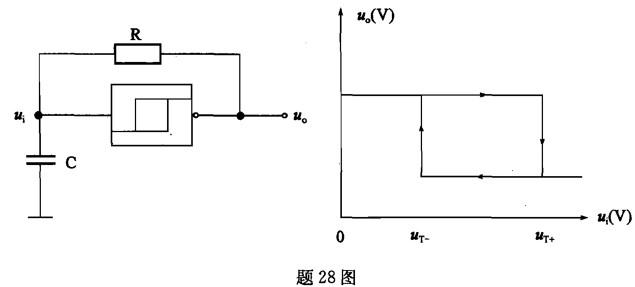

由CMOS集成施密特触发器组成的电路及该施密特触发器的电压传输特性曲线如图所示,该电路组成了一个()。

A.存储器 B.单稳态触发器 C.反相器 D.多谐振荡器答案:D解析:解多谐振荡器是一种自激振荡器,通电后不需要外加触发信号,自动产生矩形脉冲,而矩形波还有丰富的高次谐波分量,称为多谐振荡器。 -

第24题:

一个只有单端输入的边沿触发器,输入信号为0,原来所处状态Q=1,在时钟信号改变时,触发器状态Q变为0,则该触发器为()。

- A、RS触发器

- B、JK触发器

- C、D触发器

- D、T触发器

正确答案:C