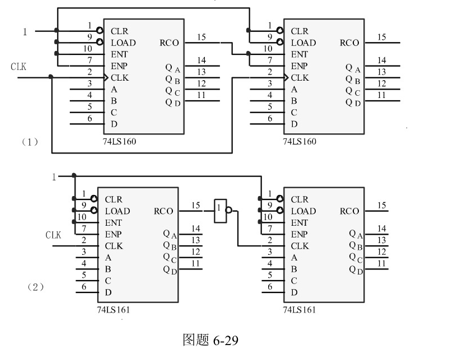

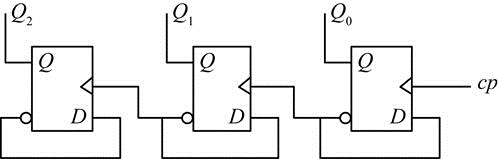

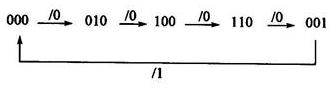

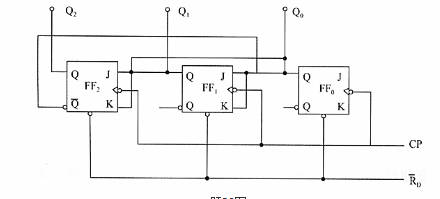

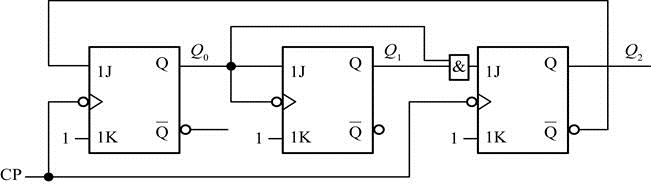

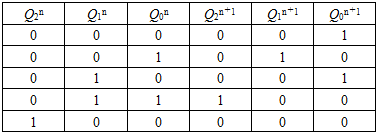

试判断图题6-29所示为电路为多少进制计数器,是同步电路还是异步电路。

题目

试判断图题6-29所示为电路为多少进制计数器,是同步电路还是异步电路。

相似考题

更多“试判断图题6-29所示为电路为多少进制计数器,是同步电路还是异步电路。 ”相关问题

-

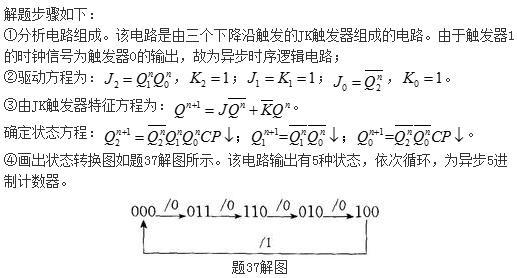

第1题:

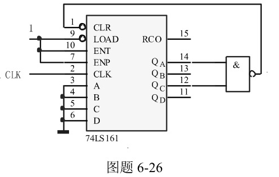

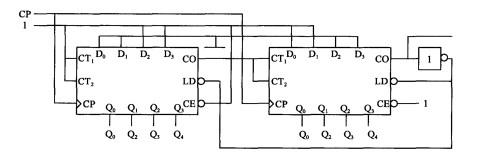

图题6-26所示为具有异步清除功能的同步四位二进制加法计数器74LS161组成的计数电路,试说明该计数电路是多少进制。

答案:异步清零5进制计数器。

答案:异步清零5进制计数器。

-

第2题:

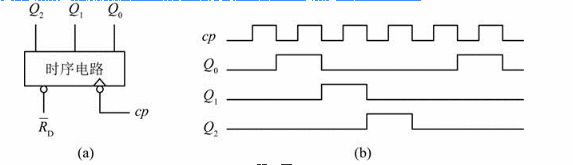

图(a)所示时序逻辑电路的工作波形如图(b)所示,由此可知,图(a)电路是一个( )。 A.右移寄存器

A.右移寄存器

B.三进制计数器

C.四进制计数器

D.五进制计数器答案:C解析:根据题96图(b)可知,时序电路的输出状态为:000—001—010—100—000—100……。因此,时序电路为四进制计数器。 -

第3题:

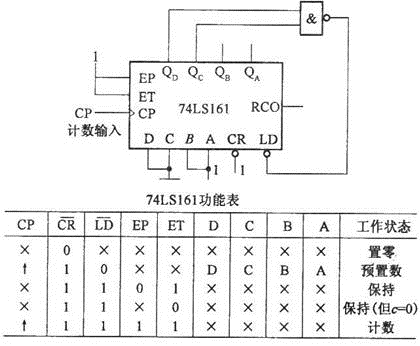

采用中规模加法计数器74LS161构成的电路如图所示,该电路构成几进制加法计数器( )。

A. 九进制

A. 九进制

B. 十进制

C. 十二进制

D. 十三进制答案:A解析:由题图中的功能表可以看出:加法计数器74LS161预置数为DCBA=(0011)2,当QD=1,QC=1首次出现时,即输出为(1100)2重新进行预置数。其它情况继续保持计数。从(0011)2到(1100)2需计数9次,因此为九进制计数器。 -

第4题:

由四位二进制同步计算器74161构成的逻辑电路如图所示,该电路的逻辑功能

为( )。

A.同步256进制计数器

C.同步217进制计数器

B.同步243进制计数器

D.同步196进制计数器答案:A解析:解 CO=Q0· Q1 · Q2 · Q3· CE

初始状态为0000?0000,当右面的计数器C0输出为1时,也就是当所有输出为1111? 1111时,整个计数器通过置数法置成0000?0000。

答案:A -

第5题:

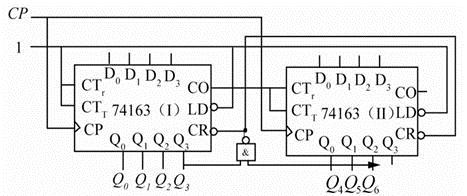

图示电路中,计数器74163构成电路的逻辑功能为( )。

A. 同步84进制加法计数

A. 同步84进制加法计数

B. 同步73进制加法计数

C. 同步72进制加法计数

D. 同步32进制加法计数答案:C解析:

-

第6题:

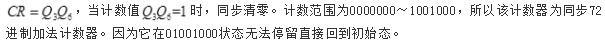

图示电路的逻辑功能为( )。

A. 异步8进制计数器

A. 异步8进制计数器

B. 异步7进制计数器

C. 异步6进制计数器

D. 异步5进制计数器答案:D解析:

-

第7题:

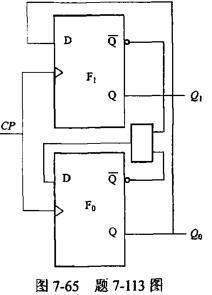

如图7-65所示电路中,两个D触发器在接受触发脉冲前为均为0,分析电路,该电路是()。

A.异步二进制计数器

B.左移计数器

C.右移计数器

D.同步三进制计数器答案:D解析:正确答案是D。

-

第8题:

时序逻辑电路的计数器直接取相应进制数经相应门电路送到()端。

- A、异步清零端

- B、同步清零端

- C、异步置数端

- D、同步置数端

正确答案:A -

第9题:

时序逻辑电路的计数器取相应进制数少一经相应门电路送到()端。

- A、异步清零端

- B、同步清零端

- C、异步置数端

- D、同步置数端

正确答案:B -

第10题:

同步二进制计数器的电路比异步二进制计数器复杂,所以实际应用中较少使用同步二进制计数器。

正确答案:错误 -

第11题:

问答题什么是同步逻辑和异步逻辑?同步电路与异步电路有何区别同步电路与异步电路有何区别?正确答案: 同步逻辑是时钟之间有固定的因果关系。异步逻辑是各时钟之间没有固定的因果关系.电路设计可分类为同步电路设计和异步电路设计。同步电路利用时钟脉冲使其子系统同步运作,而异步电路不使用时钟脉冲做同步,其子系统是使用特殊的“开始”和“完成”信号使之同步。异步电路具有下列优点:无时钟歪斜问题、低电源消耗、平均效能而非最差效能、模块性、可组合和可复用性。解析: 暂无解析 -

第12题:

单选题电路中各触发器状态改变有先有后是异步的,用它作成的计数器是()。A同步计数器

B异步计数器

C二进制计数器

D四进制计数器

正确答案: D解析: 暂无解析 -

第13题:

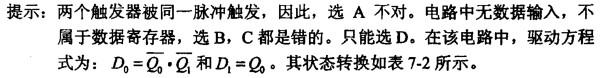

图题6-27所示为具有同步预置功能的同步四位二进制加法计数器74LS161组成的计数电路,试说明该计数电路是多少进制。

答案:该电路是同步置数6进制计数器。

答案:该电路是同步置数6进制计数器。

-

第14题:

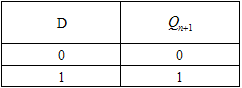

图示时序逻辑电路是一个( )。

附:触发器的逻辑状态表为:

A、左移寄存器

A、左移寄存器

B、右移寄存器

C、异步三位二进制加法计数器

D、同步六进制计数器答案:C解析:由图可知,三个触发器触发脉冲来自不同信号,且为上升沿触发,应为上升沿触发的异步计数器。

-

第15题:

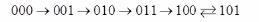

某时序电路的状态图如题图所示,则其为下列哪种电路?( )

A. 五进制计数器

A. 五进制计数器

B. 六进制计数器

C. 环形计数器

D. 移位寄存器答案:A解析:五种不重复状态完成一次循环,为五进制计数器。而环形计数器的状态为

移位寄存器有移位功能,也就是每来一个脉冲,状态向右或向左移一位,题目中从000到010的状态可知不是移位计数器。 -

第16题:

图所示逻辑电路,设触发器的初始状态均为0,当

时,该电路实现的逻辑功能是( )。 A.同步十进制加法计数器

A.同步十进制加法计数器

B.同步八进制加法计数器

C.同步六进制加法计数器

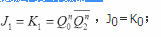

D.同步三进制加法计数器答案:C解析:①组成:该电路由于CP端连在一起,因此是同步计数器;

②列写驱动方程:J2=K2=Q1nQ0n,

③列写存储器状态方程:

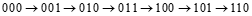

④初始值为000,计数器CP释放脉冲后,计数循环为000→001→010→011→100?101。

故为同步六进制加法计数器。 -

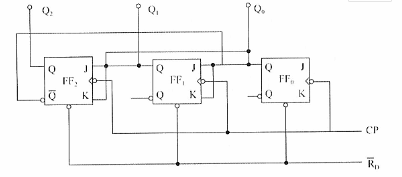

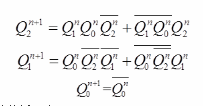

第17题:

图所示逻辑电路,设触发器的初始状态均为“0”。当RD=1时,该电路的逻辑功能为( )。 A.同步八进制加法计数器

A.同步八进制加法计数器

B.同步八进制减法计数器

C.同步六进制加法计数器

D.同步六进制减法计数器答案:C解析:①组成:该电路由于CP端连在一起,因此是同步计数器;

②列写驱动方程:

③列写存储器状态方程:

④初始值为000,计数器CP释放脉冲后,计数循环为

故为同步六进制加法计数器。 -

第18题:

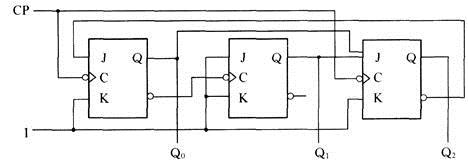

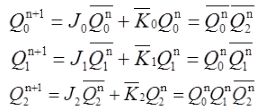

如图所示异步时序电路,该电路的逻辑功能为( )。

A. 八进制加法计数器

A. 八进制加法计数器

B. 八进制减法计数器

C. 五进制加法计数器

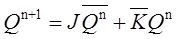

D. 五进制减法计数器答案:C解析:JK触发器的特征方程为:

可知:

故可列真值表如题解表。由真值表可知,此电路完成了5种状态的循环转换,为五进制加法计数器。

-

第19题:

下列电路中不属于时序电路的是()

- A、同步计数器

- B、数码寄存器

- C、组合逻辑电路

- D、异步计数器

正确答案:C -

第20题:

下列电路中,不属于时序逻辑电路的是()

- A、同步加法计数器

- B、全加器

- C、寄存器

- D、异步减法计数器

正确答案:B -

第21题:

电路中各触发器状态改变有先有后是异步的,用它作成的计数器是()。

- A、同步计数器

- B、异步计数器

- C、二进制计数器

- D、四进制计数器

正确答案:B -

第22题:

什么是同步逻辑和异步逻辑?同步电路与异步电路有何区别同步电路与异步电路有何区别?

正确答案:同步逻辑是时钟之间有固定的因果关系。异步逻辑是各时钟之间没有固定的因果关系.电路设计可分类为同步电路设计和异步电路设计。同步电路利用时钟脉冲使其子系统同步运作,而异步电路不使用时钟脉冲做同步,其子系统是使用特殊的“开始”和“完成”信号使之同步。异步电路具有下列优点:无时钟歪斜问题、低电源消耗、平均效能而非最差效能、模块性、可组合和可复用性。 -

第23题:

单选题下列电路中不属于时序电路的是()A同步计数器

B数码寄存器

C组合逻辑电路

D异步计数器

正确答案: B解析: 暂无解析