某型NAND Flash芯片的地址线和数据线是复用的,它具有的部分引脚为ALE、CE、RE、R/B,如果下面每一个选项是用于简述这些引脚的功能的,其中完全正确的是()A、低电平有效的芯片使能、命令锁存允许、准备就绪/忙输出、读使能/写使能B、命令锁存允许、低电平有效的写保护、低电平有效的芯片使能、地址锁存允许C、地址锁存允许、低电平有效的芯片使能、低电平有效的读使能、准备就绪/忙输出D、准备就绪/忙输出、低电平有效的读使能、低电平有效的写使能、命令锁存允许

题目

某型NAND Flash芯片的地址线和数据线是复用的,它具有的部分引脚为ALE、CE、RE、R/B,如果下面每一个选项是用于简述这些引脚的功能的,其中完全正确的是()

- A、低电平有效的芯片使能、命令锁存允许、准备就绪/忙输出、读使能/写使能

- B、命令锁存允许、低电平有效的写保护、低电平有效的芯片使能、地址锁存允许

- C、地址锁存允许、低电平有效的芯片使能、低电平有效的读使能、准备就绪/忙输出

- D、准备就绪/忙输出、低电平有效的读使能、低电平有效的写使能、命令锁存允许

相似考题

更多“某型NAND Flash芯片的地址线和数据线是复用的,它具有的部分引脚为ALE、CE、RE、R/B,如果下面每一个选项是用于简述这些引脚的功能的,其中完全正确的是()A、低电平有效的芯片使能、命令锁存允许、准备就绪/忙输出、读使能/写使能B、命令锁存允许、低电平有效的写保护、低电平有效的芯片使能、地址锁存允许C、地址锁存允许、低电平有效的芯片使能、低电平有效的读使能、准备就绪/忙输出D、准备就绪/忙输出、低电平有效的读使能、低电平有效的写使能、命令锁存允许”相关问题

-

第1题:

8031通过芯片( )和ALE信号,使P0口对应的8位地址线A7~A0锁存起来。

A.74LS273

B.74LS373

C.74LS244

D.74LS138

正确答案:B

解析:74LS373是一个锁存器,用于锁存选路信号,它还被用于产生AC01的复位信号,这些信号都由程序控制产生。 -

第2题:

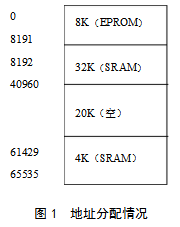

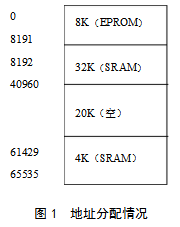

CPU的地址总线16根(A15~A0,A0是低位),双向数据总线16根(D15~D0),控制总线中与主存有关的信号 有!MREQ(允许访存,低电平有效),R/!W(高电平读命令,低电平写命令)。主存地址空间分配如下:0~8191为系统程序区,由EPROM芯片组成,从8192起一共32K地址空间为用户程序区,最后(最大地址)4K地址空间为系统程序工作区。如图1所示。上述地址为十进制,按字编址。现有如下芯片。

EPROM:8K×16位(控制端仅有!CS),16位×8位 SRAM:16K×1位,2K×8位,4K×16位,8K×16位 请从上述芯片中选择芯片设计该计算机的主存储器,画出主存逻辑框图。

EPROM:8K×16位(控制端仅有!CS),16位×8位 SRAM:16K×1位,2K×8位,4K×16位,8K×16位 请从上述芯片中选择芯片设计该计算机的主存储器,画出主存逻辑框图。

略 -

第3题:

INTEL 8088 CPU可以访问的存储器空间可达1M,使用的地址信号线为A19~A0,CPU执行一次存储器读操作时,有效控制信号是()。

- A、RD低电平,WR三态,M/IO低电平

- B、RD三态,WR低电平,M/IO高电平

- C、RD低电平,WR高电平,M/IO高电平

- D、RD高电平,WR低电平,M/IO高电平

正确答案:A -

第4题:

825lA引脚DTR是数据终端准备好信号,低电平有效,()方向,表示()准备就绪。

正确答案:输出;微处理器 -

第5题:

当集成译码器74LS138的3个使能端都满足要求时,其输出端为()有效。

- A、高电平

- B、低电平

- C、高阻

- D、低阻

正确答案:B -

第6题:

8086微处理器的RESET引脚是用于:()

- A、使CPU复位,高电平有效。

- B、CPU使其它器件复位,高电平有效。

- C、使CPU复位,低电平有效。

- D、CPU使其它器件复位,低电平有效。

正确答案:A -

第7题:

ADC0809的ALE引脚的功能是()。

- A、转换结束状态信号

- B、输出允许信号

- C、转换启动信号

- D、地址锁存允许

正确答案:D -

第8题:

LCD1602的使能端E,在引脚上出现()后,模块执行命令。

- A、低电平

- B、高电平

- C、负跳变

- D、正跳变

正确答案:C -

第9题:

MCS51中的ALE引脚的功能是:()

- A、电源正极

- B、地址锁存允许

- C、接地

- D、复位

正确答案:B -

第10题:

MCS-51的并行I/O口读-改-写操作,是针对该口的()。

- A、引脚

- B、片选信号

- C、地址线

- D、内部锁存器

正确答案:D -

第11题:

当集成译码器74LS138的三个使能端都满足要求时其输出端为()有效。

- A、高电平

- B、低电平

- C、高阻

- D、低阻

正确答案:B -

第12题:

填空题825lA引脚DTR是数据终端准备好信号,低电平有效,()方向,表示()准备就绪。正确答案: 输出,微处理器解析: 暂无解析 -

第13题:

基于嵌入式WEB的应用系统中,构件设计阶段需要设计支持以太网通信的电路,包括以太网控制电路及以太网____【39】___电路。若选用的以太网控制芯片为AX88796芯片,并用S3C2410芯片的nGCS2引脚连接到AX88796芯片的片选引脚上(即CS引脚上,CS低电平有效),那么,AX88796芯片内部寄存器的读/写地址,其首地址是___【40】____。

正确答案:驱动 0x10000000

-

第14题:

ROM中没有()。

- A、地址线

- B、数据线

- C、读使能线

- D、写使能线

正确答案:D -

第15题:

低电平有效是指信号为低电平时候表示信号的功能。

正确答案:正确 -

第16题:

关于分时复用的总线,说法不正确的是()。

- A、采用分时复用的地址数据总线可以有效减少芯片的引脚数

- B、分时复用的地址数据总线上的地址信号必须锁存

- C、为使用分时复用的地址数据总线,CPU必须提供ALE信号

- D、8086中只有分时复用的地址数据总线

正确答案:D -

第17题:

8086和8088的引脚信号中,()为地址锁存允许信号引脚。

- A、CLK

- B、INTR

- C、NMI

- D、ALE

正确答案:D -

第18题:

AT89S51引脚ALE是()

- A、程序读选通信号

- B、数据锁存允许信号

- C、地址锁存允许信号

- D、控制锁存允许信号

正确答案:C -

第19题:

共阴LED数码管在设计驱动时,应选输出()有效的驱动芯片。

- A、高阻

- B、低电平

- C、高电平

- D、任何电平

正确答案:C -

第20题:

51单片机执行MOVX写指令时,相关的信号状态是()。

- A、PSEN无效为低电平,WR有效为低电平

- B、PSEN无效为高电平,WR有效为低电平

- C、PSEN有效为低电平,WR无效为高电平

- D、PSEN有效为高电平,WR无效为高电平

正确答案:B -

第21题:

ADC0809的Start引脚的功能是()。

- A、转换结束状态信号

- B、输出允许信号

- C、转换启动信号

- D、地址锁存允许

正确答案:C -

第22题:

当74LS373输入端为高电平,使能端为低电平时其功能为()

- A、直通

- B、保持

- C、输出高阻

- D、不定

正确答案:B -

第23题:

单选题某型NAND Flash芯片的地址线和数据线是复用的,它具有的部分引脚为ALE、CE、RE、R/B,如果下面每一个选项是用于简述这些引脚的功能的,其中完全正确的是()A低电平有效的芯片使能、命令锁存允许、准备就绪/忙输出、读使能/写使能

B命令锁存允许、低电平有效的写保护、低电平有效的芯片使能、地址锁存允许

C地址锁存允许、低电平有效的芯片使能、低电平有效的读使能、准备就绪/忙输出

D准备就绪/忙输出、低电平有效的读使能、低电平有效的写使能、命令锁存允许

正确答案: B解析: NAND Flash主要用于片外程序存储器,为了节省引脚,降低体积,地址线和数据线一般采用分时复用技术。ALE、CE、RE、R/B分别表示地址锁存允许、低电平有效的芯片使能、低电平有效的读使能、准备就绪/忙输出。故C项正确。 -

第24题:

单选题对8255接口电路写一个控制命令字使其工作于方式0时,则()。A输入、输出均有锁存功能

B输出有锁存功能,输入不锁存

C输入有锁存功能,输出不锁存

D输出、输入均不锁

正确答案: A解析: 暂无解析

EPROM:8K×16位(控制端仅有!CS),16位×8位 SRAM:16K×1位,2K×8位,4K×16位,8K×16位 请从上述芯片中选择芯片设计该计算机的主存储器,画出主存逻辑框图。

EPROM:8K×16位(控制端仅有!CS),16位×8位 SRAM:16K×1位,2K×8位,4K×16位,8K×16位 请从上述芯片中选择芯片设计该计算机的主存储器,画出主存逻辑框图。